- 您现在的位置:买卖IC网 > Sheet目录3887 > PIC16F871-E/L (Microchip Technology)IC MCU CMOS 20MHZ 2K FLSH 44PLCC

PIC16F870/871

DS30569B-page 132

2003 Microchip Technology Inc.

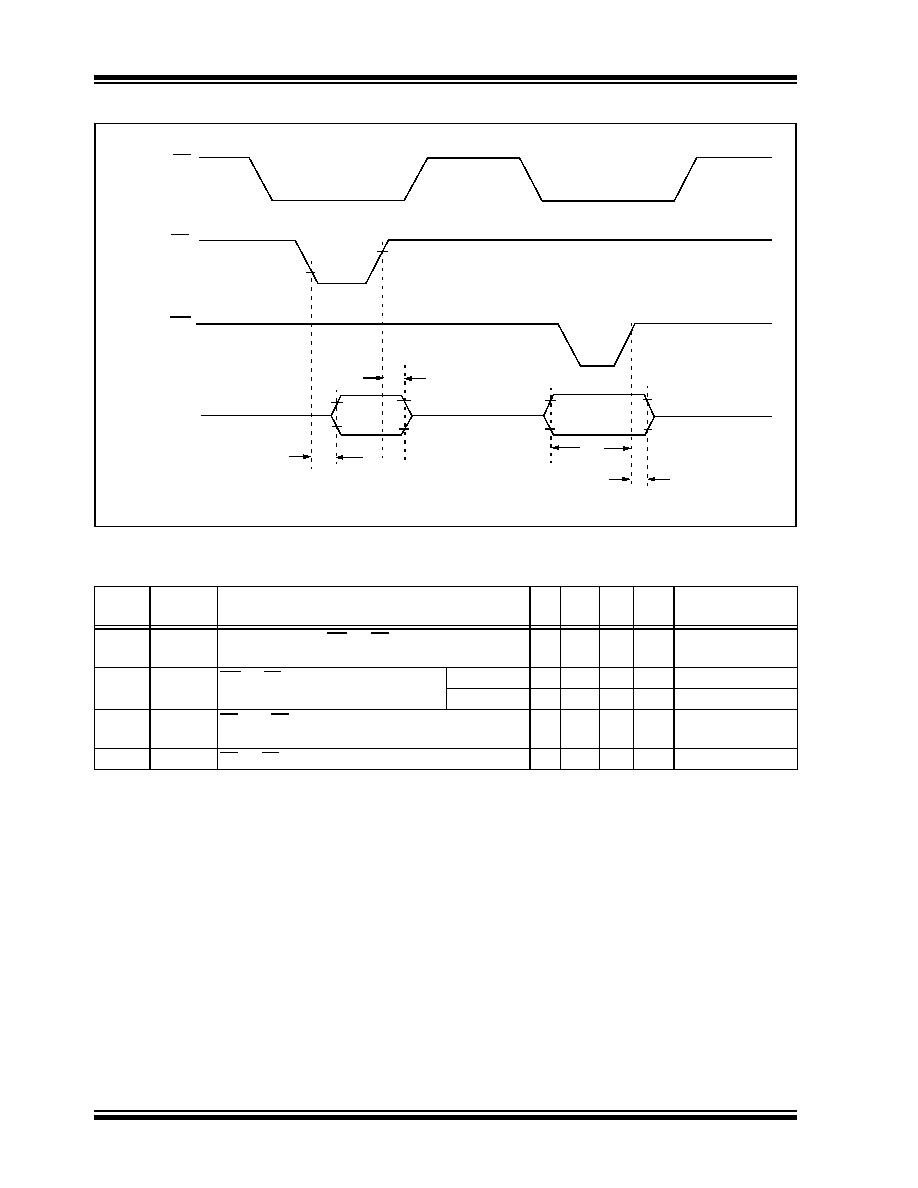

FIGURE 14-10:

PARALLEL SLAVE PORT TIMING (PIC16F871 ONLY)

TABLE 14-6:

PARALLEL SLAVE PORT REQUIREMENTS (PIC16F871 ONLY)

Note: Refer to Figure 14-3 for load conditions.

RE2/CS

RE0/RD

RE1/WR

RD7:RD0

62

63

64

65

Param

No.

Sym

Characteristic

Min Typ

Max Units

Conditions

62

TdtV2wrH

Data in valid before WR

↑ or CS↑ (setup time)

20

25

—

ns

Extended range only

63*

TwrH2dtI

WR

↑ or CS↑ to data–in invalid (hold time) Standard(F)20

—

ns

Extended(LF)35

—

ns

64

TrdL2dtV

RD

↓ and CS↓ to data–out valid

—

80

90

ns

Extended range only

65

TrdH2dtI

RD

↑ or CS↓ to data–out invalid

10

—

30

ns

*

These parameters are characterized but not tested.

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not

tested.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC16F870T-E/SS

IC MCU CMOS 20MHZ 2K FLSH 28SSOP

PIC16F870T-E/SO

IC MCU CMOS 20MHZ 2K FLSH 28SOIC

PIC16F84AT-20E/SS

IC MCU CMOS 20MHZ 1K FLSH 20SSOP

PIC16F84AT-20E/SO

IC MCU CMOS 20MHZ 1K FLSH 18SOIC

22-15-3133

CONN FFC/FPC 13POS .100 RT ANG

PIC16F84AT-04E/SS

IC MCU CMOS 4MHZ 1K FLASH 20SSOP

22-02-3133

CONN FFC/FPC VERTICAL 13POS .100

PIC16F84AT-04E/SO

IC MCU CMOS 4MHZ 1K FLASH 18SOIC

相关代理商/技术参数

PIC16F871-E/P

功能描述:8位微控制器 -MCU 3.5KB 128 RAM 33 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F871-E/PT

功能描述:8位微控制器 -MCU 3.5KB 128 RAM 33 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F871-I/L

功能描述:8位微控制器 -MCU 3.5KB 128 RAM 33 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F871-I/L

制造商:Microchip Technology Inc 功能描述:8BIT FLASH MCU SMD 16F871 PLCC44

PIC16F871-I/P

功能描述:8位微控制器 -MCU 3.5KB 128 RAM 33 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F871-I/P

制造商:Microchip Technology Inc 功能描述:IC 8BIT FLASH MCU 16F871 DIP40

PIC16F871-I/PT

功能描述:8位微控制器 -MCU 3.5KB 128 RAM 33 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F871-I/PT

制造商:Microchip Technology Inc 功能描述:8BIT FLASH MCU SMD 16F871 TQFP44